# WARSAW UNIVERSITY OF TECHNOLOGY

DISCIPLINE OF SCIENCE AUTOMATIC CONTROL, ELECTRONICS, ELECTRICAL ENGINEERING AND SPACE TECHNOLOGIES FIELD OF SCIENCE ENGINEERING AND TECHNOLOGY

# Ph.D. Thesis

Michał Kruszewski, M.Sc.

Functional Bus Description Language

Supervisor Wojciech Zabołotny, Ph.D., D.Sc

WARSAW 2024

## Abstract

Bus and register management is one of the crucial aspects of ASIC, SoC, or FPGA-based designs. The problems related to it are well known, and multiple tools or approaches are already trying to solve or mitigate them. However, all available solutions share the same register-centric paradigm. A user defines registers and then manually lays out the data into the registers. Such an approach has its limitations. A description does not contain information on data spanning multiple registers or data forming a broader context, procedure arguments, for example. It also does not contain information on the purpose of the data. As a result, the generated access code is low-level and usually needs an extra wrapper, which leaves room for potential human mistakes. For instance, it is the user's responsibility to guarantee proper access order to registers or to provide an atomic change of data wider than a single register width.

The thesis proposes a new approach, the functionality-centric approach. In the functionality-centric approach, the user defines the data with the type of its functionality. The registers and access code are later implicitly inferred. By defining the functionality of the data placed in the registers, it is possible to generate more access code, increase code robustness, improve system design readability, and shorten the implementation process.

The thesis includes the specification of the new domain-specific language (Functional Bus Description Language), presents an example of the advantages of the functionalitycentric approach compared to the register-centric, and provides reasoning for some design decisions and some compiler implementation details.

**Keywords**: bus interface, code maintenance, computer languages, control interface, design automation, design verification, documentation generation, electronic design automation, EDA, electronic systems, Functional Bus Description Language, FBDL, hardware design, hardware description language, HDL, hierarchical register description, memory, programming, register addressing, register synthesis, software generation, system management

## Streszczenie

Zarządzanie magistralą oraz rejestrami jest jednym z kluczowych aspektów podczas projektowania układów ASIC, SoC lub systemów wykorzystujących układy FPGA. Problemy z tym związane są dobrze znane. Istnieje wiele narzędzi oraz sposobów postępowania, które starają się je rozwiązywać lub niwelować ich wpływ. Wszystkie dostępne rozwiązania cechuje jednak te same podejście do zagadnienia, są one zorientowane na rejestry. Użytkownik pierw definiuje rejestr, a dopiero w kolejnym kroku ręcznie rozmieszcza w nim dane. Takie podejście zawiera pewne ograniczenia. Opis rejestrów nie zawiera informacji na temat danych znajdujących się w więcej niż jednym rejestrze, czy na temat danych będących częścią jakiegoś szerszego kontekstu, jak np. argumenty procedur. Opis nie zawiera również informacji na temat funkcjonalności jakie poszczególne dane dostarczają. W rezultacie automatycznie wygenerowany kod jest niskopoziomowy i wymaga ręcznej implementacji kodu opakowującego. To z kolei przekłada się na pozostawienie miejsca na potencjalne ludzkie pomyłki. Przykładowo, to użytkownik odpowiedzialny jest za zapewnienie poprawnej kolejności dostępów do rejestrów, czy za zapewnienie atomowości zmian wartości danych, których szerokość przekracza szerokość pojedynczego rejestru.

W rozprawie zaprezentowano nowe podejście zorientowane na funkcjonalność danych. W podejściu tym użytkownik definiuje dane wraz z ich typem funkcjonalności. Na ich podstawie są następnie automatycznie generowane rejestry wraz z kodem dostępowym. Definiowanie funkcjonalności danych pozwala na zwiększenie ilości kodu generowanego automatycznie, i zmniejszenie ilości kodu pisanego ręcznie. To z kolei zwiększa odporność kodu na błędy, poprawia czytelność projektu i skraca czas spędzony na implementacji.

Praca obejmuje specyfikację jezyka specyficznego dla danej domeny (Język Opisu Funkcjonalnych Magistral), opis korzyści wynikających z podejścia zorientowanego na funkcjonalność, uzasadnienie niektórych decyzji projektowych oraz omówienie niektórych ze szczegółów implementacji kompilatora.

Słowa kluczowe: adresowanie rejestrów, automatyzacja projektowania, magistrala, generacja oprogramowania, generacja dokumentacji, hierarchiczny opis rejestrów, interfejs sterowania, język opisu sprzętu, języki programowania, magistrala, programowanie, projektowanie sprzętu, synteza rejestrów, systemy elektroniczne, utrzymanie kodu, weryfikacja projektu, zarządzanie systemem

# Contents

| Preface  |                                  |                                                                                                                                         |                                                            |  |  |  |

|----------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| 1        | <b>Intr</b><br>1.1<br>1.2<br>1.3 | oduction         Example problem                                                                                                        | <ol> <li>14</li> <li>16</li> <li>18</li> <li>23</li> </ol> |  |  |  |

| <b>2</b> | On-                              | chip interconnect architectures                                                                                                         | 25                                                         |  |  |  |

|          | 2.1                              | AMBA AXI                                                                                                                                | 26                                                         |  |  |  |

|          | 2.2                              | Wishbone                                                                                                                                | 29                                                         |  |  |  |

|          | 2.3                              | Network on Chip                                                                                                                         | 30                                                         |  |  |  |

| 3        | Prior art                        |                                                                                                                                         |                                                            |  |  |  |

|          | 3.1                              | Existing tools                                                                                                                          | 33                                                         |  |  |  |

|          |                                  | 3.1.1 airhdl                                                                                                                            | 34                                                         |  |  |  |

|          |                                  | 3.1.2 Address Generator for Wishbone                                                                                                    | 34                                                         |  |  |  |

|          |                                  | 3.1.3 AutoFPGA                                                                                                                          | 39                                                         |  |  |  |

|          |                                  | 3.1.4 Cheby                                                                                                                             | 40                                                         |  |  |  |

|          |                                  | 3.1.5 Corsair $\ldots$                                 | 41                                                         |  |  |  |

|          |                                  | 3.1.6 Tools provided by FPGA vendors                                                                                                    | 44                                                         |  |  |  |

|          |                                  | 3.1.7 hdl_registers $\ldots$                           | 45                                                         |  |  |  |

|          |                                  | 3.1.8 II & CII                                                                                                                          | 49                                                         |  |  |  |

|          |                                  | 3.1.9 IP-XACT                                                                                                                           | 49                                                         |  |  |  |

|          |                                  | 3.1.10 Opentitan Register Tool                                                                                                          | 50                                                         |  |  |  |

|          |                                  | 3.1.11 Register Wizard                                                                                                                  | 50                                                         |  |  |  |

|          |                                  | 3.1.12 RgGen                                                                                                                            | 51                                                         |  |  |  |

|          |                                  | 3.1.13 SystemRDL                                                                                                                        | 53                                                         |  |  |  |

|          |                                  | 3.1.14 vhdMMIO                                                                                                                          | 53                                                         |  |  |  |

|          |                                  | $3.1.15 \text{ wbgen}2 \ldots \ldots$ | 55                                                         |  |  |  |

|          |                                  | 3.1.16 Others                                                                                                                           | 56                                                         |  |  |  |

|          | 3.2                              | Summary                                                                                                                                 | 56                                                         |  |  |  |

| 4        | sertation                        | 58                                                                                                                                      |                                                            |  |  |  |

|          | 4.1                              | Thesis                                                                                                                                  | 58                                                         |  |  |  |

|          | 4.2  | Aim ai                     | nd scope                            | . 58 |  |  |  |  |  |  |

|----------|------|----------------------------|-------------------------------------|------|--|--|--|--|--|--|

| <b>5</b> | Fune | Functionality types 59     |                                     |      |  |  |  |  |  |  |

|          | 5.1  | Blackb                     | хох                                 | . 59 |  |  |  |  |  |  |

|          | 5.2  | Block                      |                                     | . 59 |  |  |  |  |  |  |

|          | 5.3  | Bus .                      |                                     | . 60 |  |  |  |  |  |  |

|          | 5.4  | Config                     | 5                                   | . 62 |  |  |  |  |  |  |

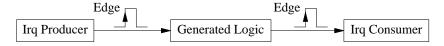

|          | 5.5  | Irq                        |                                     | . 64 |  |  |  |  |  |  |

|          | 5.6  | Mask .                     |                                     | . 64 |  |  |  |  |  |  |

|          | 5.7  | Memor                      | ry                                  | . 65 |  |  |  |  |  |  |

|          | 5.8  | Param                      | 1                                   | . 69 |  |  |  |  |  |  |

|          | 5.9  | Proc .                     |                                     | . 69 |  |  |  |  |  |  |

|          | 5.10 | Return                     | n                                   | . 70 |  |  |  |  |  |  |

|          | 5.11 | Static                     |                                     | . 70 |  |  |  |  |  |  |

|          | 5.12 | Status                     | 3                                   | . 71 |  |  |  |  |  |  |

|          | 5.13 | Stream                     | n                                   | . 71 |  |  |  |  |  |  |

| 6        | Lang | anguage absent features 72 |                                     |      |  |  |  |  |  |  |

|          | 6.1  | Two-w                      | vriter data                         | . 72 |  |  |  |  |  |  |

|          | 6.2  | Enume                      | eration type                        | . 73 |  |  |  |  |  |  |

|          | 6.3  | Custor                     | m expression functions              | . 75 |  |  |  |  |  |  |

|          | 6.4  | Manua                      | al addressing                       | . 76 |  |  |  |  |  |  |

|          | 6.5  | Custor                     | m attributes                        | . 76 |  |  |  |  |  |  |

| 7        | Con  | Compiler implementation 77 |                                     |      |  |  |  |  |  |  |

|          | 7.1  | Front-e                    | end                                 | . 78 |  |  |  |  |  |  |

|          |      | 7.1.1                      | Description file parsing            | . 79 |  |  |  |  |  |  |

|          |      | 7.1.2                      | Functionality instantiation         | . 79 |  |  |  |  |  |  |

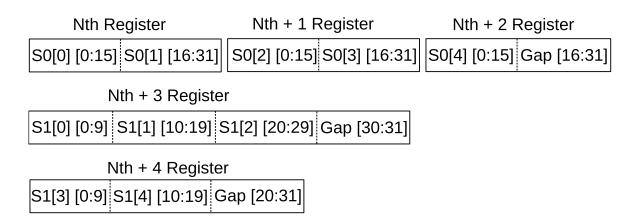

|          |      | 7.1.3                      | Functionality registerification     | . 79 |  |  |  |  |  |  |

|          | 7.2  | Back-e                     | end                                 | . 87 |  |  |  |  |  |  |

| 8        | Exa  | ample design 92            |                                     |      |  |  |  |  |  |  |

|          | 8.1  |                            |                                     |      |  |  |  |  |  |  |

|          |      | 8.1.1                      | Automatic data placement (MT)       |      |  |  |  |  |  |  |

|          |      | 8.1.2                      | Automatic array handling (MRT)      |      |  |  |  |  |  |  |

|          |      | 8.1.3                      | Access atomicity (MST)              |      |  |  |  |  |  |  |

|          |      | 8.1.4                      | Procedure and stream contexts (MRS) |      |  |  |  |  |  |  |

|          |      | 8.1.5                      | Additional types (R)                |      |  |  |  |  |  |  |

|          | 8.2  |                            | esis results                        |      |  |  |  |  |  |  |

|          |      | - ,                        |                                     |      |  |  |  |  |  |  |

| 9            | Real use case                                                     | 122 |  |

|--------------|-------------------------------------------------------------------|-----|--|

| 10           | Summary                                                           | 123 |  |

| Aŗ           | Appendices                                                        |     |  |

| $\mathbf{A}$ | Supervisor registerification results                              | 138 |  |

| в            | Example design registerification results                          | 141 |  |

| $\mathbf{C}$ | Example design register map                                       | 145 |  |

| D            | Python code automatically generated for the example design        | 146 |  |

| $\mathbf{E}$ | VHDL Main entity description generated for the example design     | 160 |  |

| $\mathbf{F}$ | VHDL Subblock entity description generated for the example design | 163 |  |

| $\mathbf{G}$ | Statement from the Fluence company                                | 166 |  |

| н            | FBDL Specification                                                | 168 |  |

## List of abbreviations

- AGWB Address Generator for Wishbone

- AMBA ARM Advanced Microcontroller Bus Architecture

- AMD Advanced Micro Devices

- **API** Application Programming Interface

- ASIC Application-Specific Integrated Circuit

- **AXI** Advanced eXtensible Interface

- **BFM** Bus Functional Model

- **CBM** Compressed Baryonic Matter

- **CDC** Clock Domain Crossing

- **CPU** Central Processing Unit

- **CMS** Compact Muon Solenoid

- **CSV** Comma-Separated Values

- **DAQ** Data Acquisition

- **DESY** Deutsches Elektronen-Synchrotron

- EDA Electronic Design Automation

- EISA Extended Industry Standard Architecture

- FBDL Functional Bus Description Language

- FIFO First In, First Out

- FPGA Field Programmable Gate Array

- **GPIO** General-Purpose Input/Output

- **GUI** Graphical User Interface

- HDL Hardware Description Language

- **HEP** High Energy Physics

- HLS High Level Synthesis

HTML HyperText Markup Language

**IBM** International Business Machines Corporation

**IO** Input/Output

**IP** Intellectual Property / Internet Protocol

**ISA** Industry Standard Architecture

JSON JavaScript Object Notation

${\bf LAN}\,$  Local Area Network

LSB Least Significant Bit

${\bf LUT}$  Lookup Table

MCA Micro Channel Architecture

$\mathbf{MCU}$  Microcontroller Unit

MMIO Memory Mapped Input Output

NoC Network on Chip

${\bf OSD}\,$  Open Software Description Data

**PCI** Peripheral Component Interconnect

**PCIe** Peripheral Component Interconnect Express

**POSIX** Portable Operating System Interface for UNIX

SCSI Small Computer Systems Interface

**SLR** Super Logic Region

SoC System on Chip

**SPI** Serial Peripheral Interface

**STS** Silicon Tracking System

SystemRDL System Register Description Language

**TCP** Transmission Control Protocol

TOML Tom's Obvious, Minimal Language

**UART** Universal Asynchronous Receiver-Transmitter

${\bf URL}\,$  Uniform Resource Locator

**UVVM** Universal VHDL Verification Methodology

- **USB** Universal Serial Bus

- **UVM** Universal Verification Methodology

- ${\bf VESA}~{\rm Video}$  Electronics Standards Association

- **VHDL** Very High Speed Integrated Circuit Hardware Description Language

- **WAN** Wide Area Network

- ${\bf XLS}~{\rm Excel}~{\rm Spreadsheet}$

- ${\bf XML}\,$ Extensible Markup Language

#### YAML YAML Ain't Markup Language

# Preface

#### Context and motivation of the dissertation

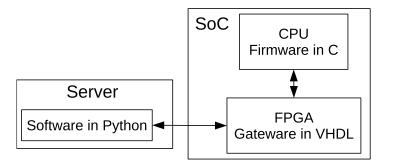

Designing, implementing, and integrating FPGA-based designs with a software stack running on a traditional CPU or a firmware stack running on an MCU poses a relatively complex technological, organizational, and methodical task. DAQ systems for HEP experiments, among military, medical, and digital entertainment systems, are examples of areas where such tasks are omnipresent and inevitable.

The author of the dissertation, for four years, has been taking part in the design and implementation process of the gateware, firmware, and software for the DAQ system for the CBM [1] experiment that has been prepared at the GSI Helmholtzzentrum für Schwerionenforschung in Darmstadt [2].

Design environments for DAQ systems in HEP experiments are very peculiar. The whole design and implementation take relatively long, from a few to even a dozen or so years. The engineering teams are international. The educational background is varied. There are physicists, electronics engineers, computer science engineers, system administrators, etc. The spectrum of the members' ages is vast, ranging from first-year Ph.D. students to halftime retired workers. Most members participate in multiple projects or have academic duties, so the time they devote to a particular task is limited. During the development phase, there is also a rotation of the employees. As a whole system is extensive and complex and must work reliably, it is natural that the preliminary prototypes vary significantly from the final solutions. All of this leads to implementing the same or similar functionalities multiple times. For example, a programming language change after the prototyping stage forces such reimplementation.

During the first two years of the studies, the author explored how to make such complex and multidimensional projects more manageable and verifiable. Trying to incorporate some industrial methodologies, such as UVM framework or formal verification, simply failed. There were at least several reasons for this. To name a few:

- Lack of free, open source tools or limited functionality of such tools. Paid commercial tools have expensive licenses.

- Too steep learning curve and lack of learning resources. The EDA tools appear to be inadequate for engineers who do not use them every day for eight hours. Instead

of focusing on the design and fundamental problems, one spends time learning how to use the EDA tools, each with a distinct user interface.

Throughout the work, it turned out that another policy is suited much better in such a diverse environment. Instead of incorporating cumbersome industrial standards that need expensive licenses, one can automatically generate as much gateware, firmware, and software as possible. As long as the description format is easily readable by a human, the work is moving forward surprisingly fast.

Based on this observation, the author has been looking for a way to enhance and extend existing generic methods and tools commonly used for gateware, firmware, and software code generation. During the work on the AGWB [3], and after using it for a few months, the author noticed that a relatively large amount of code was still repeatedly implemented manually. That manually implemented code had some common characteristics and could be easily automatically generated. The only thing that needed to be added to generate it was the information on the functionality that a given data must serve. That required shifting the accent from the register (register-centric approach) to the data or, more precisely, to the functionality of the data (functionality-centric approach). After analyzing state-of-the-art tools and approaches, the author concluded that no solution is based on the data functionality paradigm. The author has decided that the idea is worth trying, and the FBDL realizes this idea.

#### Structure of the thesis

The thesis consists of 10 chapters and 8 additional appendices. Appendix G is the specification of the newly defined Functional Bus Description Language. It is advised to at least skim it before reading the dissertation and later return to it while reading chapter 5. The specification also includes definitions of some terms used in the thesis.

Chapter 1 introduces the bus and register management problem. It provides a simplified example that is used to present some of the subproblems and analyze how they are solved in the register-centric (typical) approach and functionality-centric (newly proposed) approach.

Chapter 2 briefly discusses on-chip interconnect architectures. It uses AMBA AXI and Wishbone buses to present two distinct bus control logics. It also discusses the NoC technology, a natural progression of traditional on-chip buses.

Chapter 3 is the prior art analysis. It includes only solutions following the register-centric paradigm. The author proposes a paradigm shift to the functionality, and no solution following this approach has been found.

Chapter 4 contains the definition of the thesis. Then, the aim and scope of the dissertation is described.

Chapter 5 serves as an extension to the FBDL specification. It discusses all supported functionalities, and unlike the specification, it focuses on answering the "why" questions instead of the "how" questions. It is recommended to read subsections of this chapter concurrently with the corresponding subsections of the FBDL specification (first specification, then dissertation) or to read the whole specification first.

Chapter 6 discusses the most common features present in the register-centric tools but absent in the FBDL. The focus is on reasoning why they are absent at the current stage of the language.

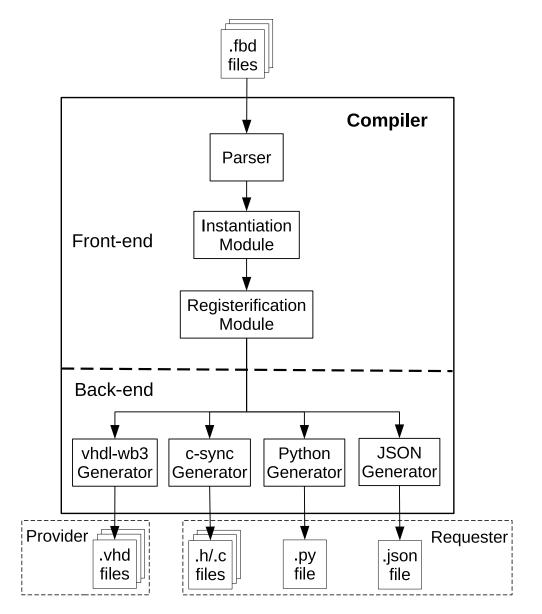

Chapter 7 describes the implementation of the compiler for the FBDL. As the comprehensive description would be relatively long and include aspects irrelevant from the thesis point of view, the chapter describes only the overall structure and focuses on some general details that any FBDL-compliant compiler will likely have to face.

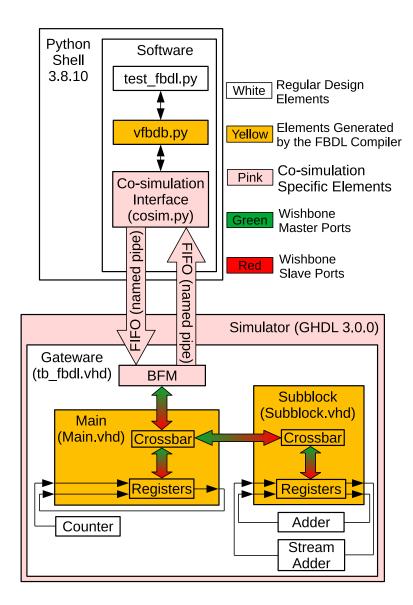

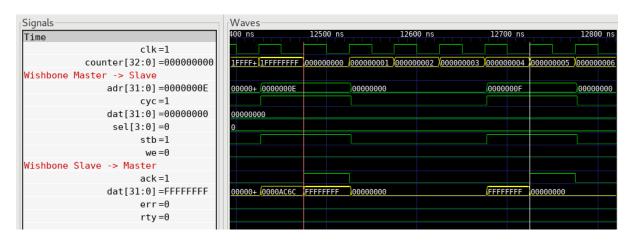

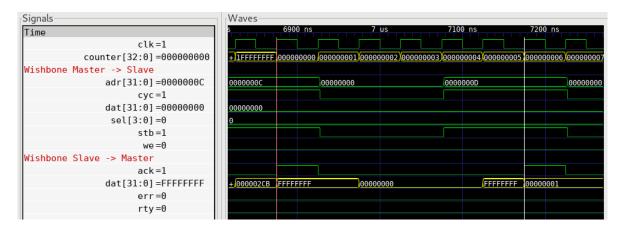

Chapter 8 compares two descriptions of the same example system. One of the descriptions follows the register-centric approach, while the other follows the functionality-centric approach. Both descriptions have been tested using co-simulation testbenches. They have also been synthesized to compare resource utilization. The chapter contains multiple listings and waveforms presenting how the functionality-centric approach can decrease the probability of human mistakes and shorten the time required to implement the system.

Chapter 9 provides information on the project in which FBDL has been used. However, due to the proprietary nature of the project, no internal details are revealed.

Chapter 10 summarizes the advantages of describing system bus registers using the functionality-centric approach instead of the register-centric.

The thesis has numerous code snippets and listings used as examples to illustrate problems better or explain solutions. The VHDL language has been chosen for the gateware, and the Python language has been chosen for the software. However, all presented concepts are programming language agnostic, so any language could be selected, and the reasoning would remain valid.

# **1** Introduction

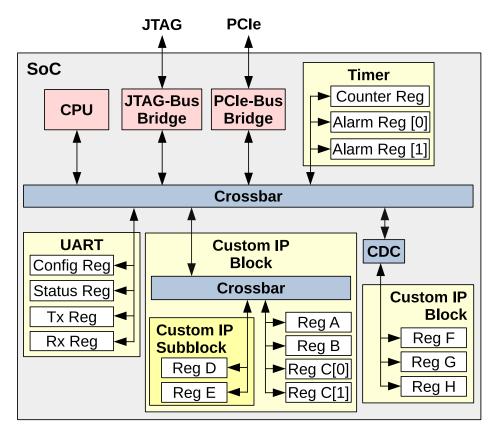

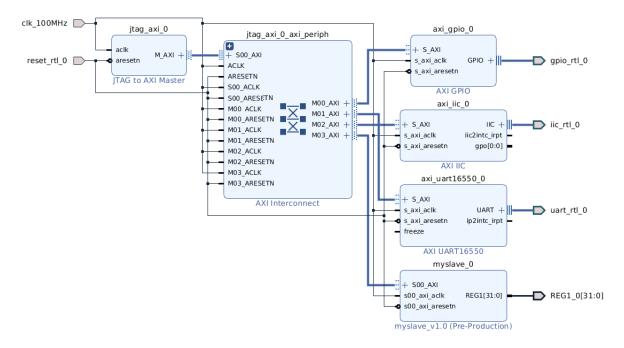

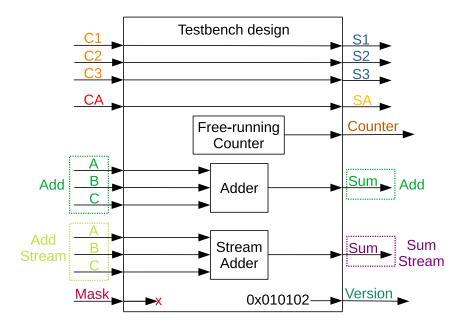

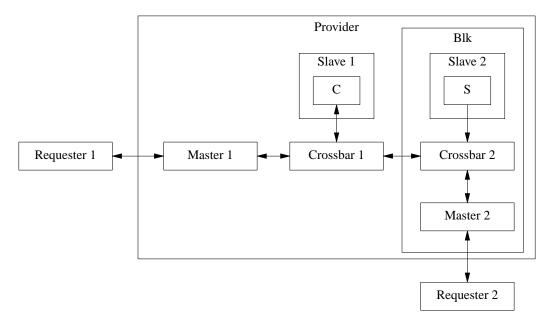

Most ASIC, FPGA, or SoC designs, for sure the more complex ones, have some kind of internal bus. Such a bus is often referred to as a "system bus," "local bus," "on-chip bus," "interconnect bus," or "on-chip interconnect bus" (the last one is the most formal and probably the most appropriate). The primary role of the bus is to provide an organized and structured manner for connecting independent modules within the chip. It also serves as a gateway to access the gateware or hardware design internals from the firmware or software stack. Such access includes writing control signals, reading status signals, bi-directional data streaming, procedure triggering, interrupt signaling, etc. Figure 1.1 presents an example of a simplified structure of some SoC. Master modules are red, slave modules are yellow, and bus fabric components are blue.

Figure 1.1: Example internal structure of some SoC design with bus.

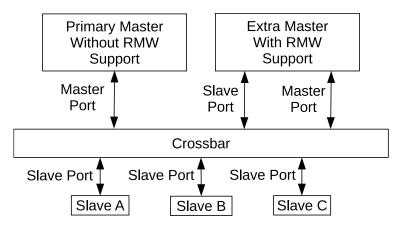

A bus usually consists of an address bus, a data bus, and a control bus. The most popular on-chip buses used in FPGA designs are probably AXI [4] (which is part of the AMBA) and Wishbone [5]. If there is a bus in a design, then the bus needs to be managed. The bus management consists of the following logical elements:

- 1. Address space management. This includes:

- a) Assigning address ranges to the modules.

- b) Aligning address ranges according to the user's policy.

- 2. Bus fabric management. This includes:

- a) Description of the modules hierarchy.

- b) Generation of the bus fabric components (such as crossbars) according to the user-provided description.

- 3. Registers management. This includes:

- a) Ordering registers within the modules.

- b) Splitting long signals between multiple registers.

- c) Grouping short signals into a single register.

- d) Attributing additional functions to the registers, such as associated strobe or acknowledgment signals.

All bus and register management tasks can be done manually, semi-automated, or fully automated. The greater the automation, the less room for potential engineers' mistakes and the greater the pace of the project development.

Managing the bus in a complex system is a well-known and non-trivial problem, especially in hardware-software co-design projects [6, 7, 8, 9, 10, 11]. Even though various approaches and implementations have already been proposed, there is still no solution that would make the bus management process fully automated. All available tools and standards either only support some of the logical elements of bus management or require users to do the register management manually. The register management is the bus management's most time-consuming and error-prone part. What is more, when the register logic is not fully automatically generated, there is a need to verify the behavior of the registers. This is usually done in simulation by directed or randomized testbenches. However, [12] presents the benefits of doing register verification using formal methods, and [13] shows an example implementation of this idea.

## 1.1 Example problem

The following section introduces an example to ease the reasoning. The example also presents the typical register-centric approach for managing registers and the new functionality-centric approach proposed in the thesis. It presents some, but not all, problems encountered in a register-centric approach that are eliminated in the newly proposed approach.

Let us assume there is a module implemented in the FPGA logic called the *Supervisor*. The Supervisor is capable of scheduling work to be done by some *Worker* modules. The Supervisor has a 48-bit internal counter that can be reset. The Supervisor can pass data to Worker modules at programmed counter value. There are 24 workers, and the data passed to them is two 12-bit long vectors. The data might be passed to any set of workers. For simplicity, let us assume that the data passed to all the workers is the same. The Supervisor also has two additional status bits, informing whether it is currently programmed (the data is scheduled to be processed) and whether it has been programmed in the past. Programming in the past means that the Supervisor will not fire data passing to the Workers before counter overflow. The Supervisor can also be unprogrammed. Listing 1 shows the VHDL interface of the example Supervisor. Signals connected to the particular ports have analogous names without the \_i and \_o suffixes.

Inside an FPGA, is a 32-bit wide bus (this is the width of the data; the width of the address is irrelevant in this consideration). What bus it is and how it can be accessed from the software is irrelevant to the analysis. A proper interface for accessing the bus is provided via the registers\_handle parameter.

The example Supervisor must be controlled by the software running on a CPU. Listing 2 shows an example Python interface of the Supervisor.

```

entity Supervisor is

generic (WORKER_COUNT : positive := 24);

port (

clk_i : in std_logic;

-- Supervisor control interface

: out std_logic_vector(47 downto 0);

counter_o

reset_counter_i : in std_logic;

-- Program procedure

program_i

: in std_logic;

programmed_counter_value_i : in std_logic_vector(47 downto 0);

worker_data0_i

: in std_logic_vector(11 downto 0);

worker_data1_i

: in std_logic_vector(11 downto 0);

-- Workers mask is set independently

workers_mask_i : in std_logic_vector(WORKER_COUNT-1 downto 0);

-- Unprogram procedure

unprogram_i : in std_logic;

-- Status bits

programmed_o

: out std_logic;

programmed_in_past_o : out std_logic;

workers_ready_o

: out std_logic_vector(WORKER_COUNT-1 downto 0);

-- Interface to Workers

workers_ready_i : in std_logic_vector(WORKER_COUNT-1 downto 0);

data_valid_o

: out std_logic_vector(WORKER_COUNT-1 downto 0);

worker data0 o : out std logic vector(11 downto 0);

worker_data1_o : out std_logic_vector(11 downto 0)

);

end entity;

```

Listing 1: Example Supervisor VHDL entity interface.

```

class Supervisor():

def __init__(self, registers_handle):

pass

def read_counter(self):

pass

def reset_counter(self):

pass

def read_status_bits(self):

pass

def program(self, counter_value, worker_data0, worker_data1):

pass

def unprogram(self):

pass

def read_workers_ready(self):

pass

def set_workers(self, workers):

pass

```

Listing 2: Example Supervisor Python software interface.

#### 1.2 Register-centric approach

In the register-centric approach, one has to take the following mandatory steps:

- a) Identify control signals. In the case of the Supervisor, these are: reset\_counter, program, unprogram, programmed\_counter\_value, worker\_data0, worker\_data1, workers\_mask.

- b) Identify status signals. In the case of the Supervisor, these are: counter, programmed, programmed\_in\_past, workers\_ready.

- c) Identify which control signals form a broader context. For instance, worker\_data0 does not make sense when used alone. It is solely one of the procedure's parameters allowing for passing data to the workers. On the other hand, unprogram makes sense on its own.

- d) Identify which status signals form a broader context. There is no such case in the example Supervisor.

- e) Calculate the number of bits required for control and status signals. The example Supervisor needs 82 status bits (counter, programmed, programmed\_in\_past, workers\_ready) and 96 control bits (programmed\_counter\_value, worker\_data0, worker\_data1, workers\_mask). Whether reset\_counter, program, unprogram should be included is yet another question. As these are single-bit signals solely triggering some action, they can be implemented as registers or fields requiring explicit set and clear or as register-associated signals triggered during register write. The second option is usually better as it provides lower latency. However, if the first option is chosen, then there are 99 control bits.

- f) Identify control and status signals requiring special handling. For example, in the case of the Supervisor, there is 48-bit long counter value. As the bus width is 32 bits, one needs to provide some mechanism for an atomic read of the counter value to keep the value integrity while reading the counter.

- g) Manually decide the register layout. This step involves answering a lot of irrelevant questions. For example, how many registers are needed? Should lower bits of the counter value be placed in the first or the second status register? Should reading the first or the second register of the counter value trigger the atomic read? Should programmed and programmed\_in\_past be placed in separate registers or in one of the counter value registers to save some address space size? What should be the order of control signals within the control registers? The number of possible implementations is infinite.

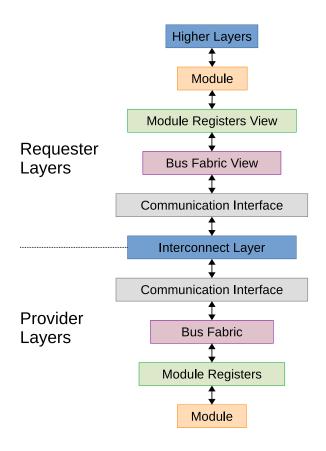

It is quite a lot of work, even for such a simple module. Moreover, the whole register structure must also be reflected in the software. Figure 1.2 shows a conceptual model of layers in the register-centric approach.

Figure 1.2: Conceptual stack of layers in the register-centric approach.

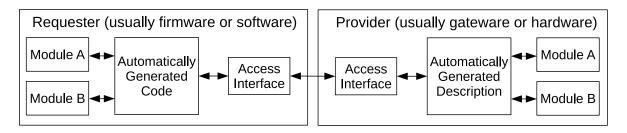

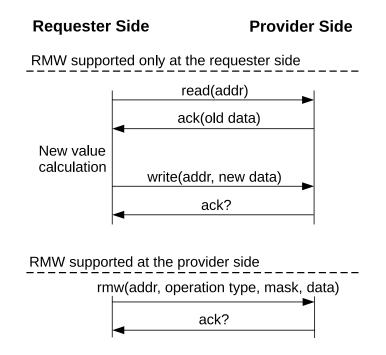

The communication interface and interconnect layers are irrelevant regarding the address space and register management. Register-centric solutions focus on the module registers and bus fabric layers. They allow describing one or more of these layers and can autogenerate appropriate gateware, firmware, and software. However, these solutions ignore the fact that some signals might need special handling or be a part of some broader context. For instance, a user has to implement atomic reads or writes himself. The same applies to the software responsible for triggering procedures implemented in the gateware, consisting of multiple control registers. Such an approach is error-prone and leads to duplication of information. For example, the information that some signal needs atomic read is manually implemented in two places: in the firmware source code and the software source code.

Working manually on the register layout is also susceptible to changes. In the example Supervisor module, there are 96 bits needed for the control signals if reset\_counter, program, and unprogram are implemented as strobe signals associated with given con-

trol registers. This is exactly three registers on a 32-bit wide bus. However, should reset\_counter, program, unprogram be associated with registers storing some data, or maybe with virtual registers (registers with addresses but not storing any data)? What happens if more workers have to be added? The user has to manually add more control registers and adjust the firmware and software accordingly. Yet another question arises. Should the whole, longer workers\_mask be moved to the new third control register, or maybe just the new extra bits? Listing 3 shows an example implementation of the software handling Supervisor module in the case of a register-centric approach.

```

class Supervisor:

def __init__(self, registers_handle):

self.registers_handle = registers_handle

def read_counter(self):

""" To keep counter integrity and perform atomic read, the

counter register 0 must be read as the first one. """

counter = self.registers_handle.Counter0.read()

counter |= self.registers handle.Counter1.read() << 32</pre>

return counter

def reset_counter(self):

self.registers_handle.Reset_Counter.write(0)

def read status bits(self):

""" Returns tuple (programmed, programmed_in_past). """

status = self.registers_handle.Status.read()

return status & 1, status & 2

def program(self, counter_value, worker_data0, worker_data1):

""" ProgramO register has to be written as the last one, as it has

strobe signal associated with it, which serves as the arm signal. """

self.registers_handle.Program2.write((worker_data1 << 12) | worker_data0)</pre>

self.registers_handle.Program1.write(counter_value >> 32)

self.registers_handle.ProgramO.write(counter_value & 0xFFFFFFFF)

def unprogram(self):

self.registers_handle.Unprogram.write(0)

def read_workers_ready(self):

return self.registers_handle.Workers_Ready.read()

def set_workers(self, workers):

""" Enable given workers. Workers argument can be a worker number

or a list of workers numbers. """

if type(workers) == int:

workers = [workers]

mask = 0

for w in workers:

mask \mid = 1 \ll w

self.registers_handle.Workers_Mask.write(mask)

```

Listing 3: Example Supervisor software interface implementation for register-centric approach.

It all has to be coded manually. What is worse is that in case of any register changes, it also has to be adjusted manually. This is because available solutions are register-centric. They treat registers as a goal, not as a path to an actual goal, which is always the functionality of the data.

The register-centric approach gives much freedom and is highly flexible. On the other hand, it does not look at the registers from the broader context and is unaware of the semantics of the stored data. This implies micro-management of registers, generates a lot of irrelevant questions, and is relatively susceptible to changes.

Listing 5 presents an example SystemRDL description for the example Supervisor. SystemRDL is the only formally defined register-centric format. If there were a need to increase the number of workers above the data bus width, then the description would need a relatively lot of adjustments. The register layout is described manually, so the WORKER\_COUNT macro can no longer be used. Listing 4 presents the file difference that would have to be applied in such a case.

```

5,6d4

<

`define WORKER_COUNT 24

<

19,20c17,21

field {fieldwidth = `WORKER_COUNT; sw = w; hw = r;} mask;

<

<

} Workers_Mask;

_ _ _

>

field {sw = w; hw = r;} mask;

} Workers Mask0;

>

>

reg {

field {fieldwidth = 1; sw = w; hw = r;} mask;

>

} Workers Mask1;

>

37,38c38,42

field {fieldwidth = `WORKER_COUNT; sw = r; hw = w;} mask;

<

<

} Workers_Ready;

___

field {sw = r; hw = w;} mask;

>

>

} Workers_Ready0;

>

reg {

field {fieldwidth = 1; sw = r; hw = w;} mask;

>

>

} Workers_Ready1;

```

Listing 4: Example Supervisor SystemRDL description change for worker count increase above the data bus width.

```

addrmap Supervisor {

name = "Supervisor";

default regwidth = 32;

`define WORKER_COUNT 24

reg empty_strobe_reg_t {

field {sw = w; hw = na; swacc;} dummy;

};

// CounterO has to be read as the first one to

// keep counter value integrity.

reg { field { sw = r; hw = w; } data; } Counter0;

reg {

regwidth = 16;

field {sw = r; hw = w;} data[16];

} Counter1;

empty_strobe_reg_t Reset_Counter;

reg {

field {fieldwidth = `WORKER_COUNT; sw = w; hw = r;} mask;

} Workers_Mask;

// ProgramO must be written as the last one,

// as the write triggers Program procedure.

reg {

field {sw = w; hw = r; swacc;} counter_value0;

} Program0;

reg {

regwidth = 16;

field {sw = w; hw = r;} counter_value1[16];

} Program1;

reg {

field {sw = w; hw = r;} worker_data0[12];

field {sw = w; hw = r;} worker_data1[12];

} Program2;

empty_strobe_reg_t Unprogram;

reg {

field {fieldwidth = `WORKER_COUNT; sw = r; hw = w;} mask;

} Workers_Ready;

reg {

field {fieldwidth = 1; sw = r; hw = w;} programmed;

field {fieldwidth = 1; sw = r; hw = w;} programmed_in_past;

} Status;

};

```

```

Listing 5: Example Supervisor SystemRDL description.

```

## **1.3 Functionality-centric approach**

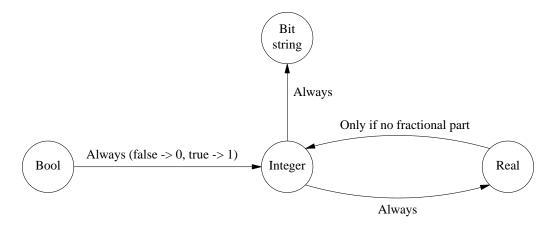

The thesis proposes a paradigm shift leading to a different approach. It looks at the design and modules from the *functionality* point of view. It is the functionality of the data that is in the center. An engineer always thinks about the functionality a given module should serve. The whole register layout is automatically generated based on the declarative description of the provided functionalities.

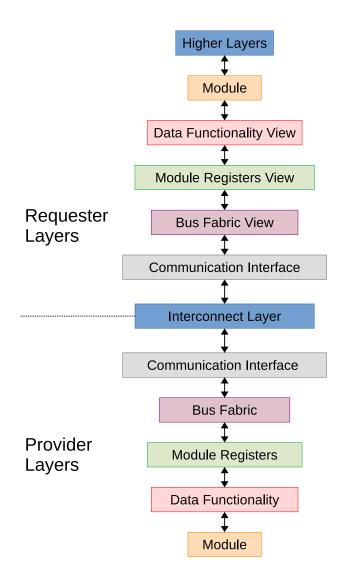

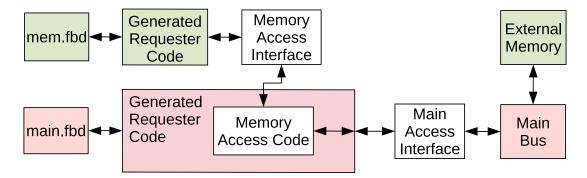

Figure 1.3 shows a conceptual model of layers in the functionality-centric approach. There is an extra data functionality layer compared to the register-centric approach. This is the core layer in this model. The module register layers are automatically generated based on the data functionality layer.

Figure 1.3: Conceptual stack of layers in the functionality-centric approach.

Looking at data from the functionality point of view allows for avoiding register micromanagement. Having functionality embedded into the register data notation also helps to prevent information duplication. For example, atomic accesses or procedure calls can be easily automatically generated for both the requester and the provider. This removes a whole surface of potential human mistakes.

Listing 6 presents FBDL description for the example Supervisor, and appendix A presents registerification results. If there were a need to change the number of workers, then it would be enough to change the WORKER\_COUNT constant value, even if the new number was greater than the bus width. Listing 7 presents the file difference that would have to be applied in such a case. As the compiler carries out the registerification process, the whole register layout is automatically adjusted. There is no need to manually adapt gateware, firmware, or software code. As FBDL promotes safety by default, there is also no need to explicitly declare Counter status to be atomic. Any data wider than the data bus width has atomic access unless explicitly waived by the user.

```

Main bus

Supervisor block

const WORKER_COUNT = 24

Counter status; width = 48

Reset_Counter proc

Workers_Mask mask; width = WORKER_COUNT

Program proc

counter_value param; width = 48

worker_data [2]param; width = 12

Unprogram proc

Workers_Ready status; width = WORKER_COUNT

type status_t status; width = 1; groups = "status"

programmed status_t

```

Listing 6: Example Supervisor FBDL description.

3c3 < const WORKER\_COUNT = 24 ---> const WORKER\_COUNT = 33

Listing 7: Example Supervisor FBDL description change for worker count increase above the bus width.

# 2 On-chip interconnect architectures

Probably every practical computing system ever created consists of independent components (there is at least some processing unit and a memory). In order to achieve synergy and serve desired functionality, these components must communicate with each other using a set of organized rules (communication protocols or standards). This network of connections is often referred to as system interconnect. The very first interconnect architectures were also called buses. The term "bus" originates from the computer, whose history can be traced back to 1946 [14]. This term is still in common use, although nowadays, bus protocols differ significantly from their ancestors. A bus, in general, is a common pathway through which information flows from one computer component to another. In the early days, computer components were relatively big, and all buses were physically made of copper wires, or later as traces on the printed circuit boards. Initially, those buses served four functions:

- 1. Data sharing the primary purpose of every bus. Data processing is the core concept of every computing system. It would not be achievable without data transfer between system components.

- 2. Addressing a bus had address lines. This allowed data to be sent to a particular system component to a specific memory location.

- 3. Clock distribution a bus provided a system clock signal to synchronize the peripherals attached to it or even to clock the peripheral itself.

- 4. Power supplying a bus supplied power to various peripherals connected to it.

The most popular computer expansion buses include ISA [15], EISA [16], MCA [17], VESA [18], SCSI [19], USB [20], and PCI/PCIe [21]. Most of them are not used anymore as they have been replaced with the USB and PCIe. With the advancement of technology, especially integrated circuits technology, it was possible to shrink components of computing systems to the sizes, allowing the placement of multiple of them (or even the whole system) on a single chip. There was still a need to connect system components to enable communication between them. However, traditional microcomputer buses were fundamentally handicapped for use as a SoC interconnection. This is because they were designed to drive long signal traces and connector systems, which are highly inductive and capacitive. In this regard, SoC is much simpler and faster. Furthermore, the SoC solutions have a rich set of interconnection resources. These do not exist in microcomputer buses because they are limited by chip packaging and mechanical connectors. As the existing buses were not optimal for implementation on chips, the interconnect architectures started to be grouped into two classes: the off-chip interconnect architectures and the on-chip interconnect architectures. The on-chip buses serve the same functions as the off-chip buses except the last one, the power supply [22]. In the case of SoCs, the power is usually supplied separately via the chip backbone. The clock is also not always distributed, as a bus can be asynchronous [23], but this might also be valid in the case of off-chip buses. Examples of prevailing on-chip buses include ARM AMBA AXI [4], IBM CoreConnect [24], Intel Avalon [25], STMicroelectronics STBus [26], Opencores Wishbone [5], MARBLE (asynchronous) [27].

The following sections briefly describe two on-chip bus standards, the AXI and the Wishbone. They have been chosen because:

- 1. they are omnipresent and popular,

- 2. they have different control logic.

The descriptions are brief because the Wishbone revision B4 specification has 128 pages and, the AMBA AXI specification is 273 pages long. The subsections' purpose is solely to introduce example bus logic.

#### 2.1 AMBA AXI

The AMBA AXI protocol is copyrighted by the Arm company. Its first version was released in 2003, and its latest version, 5, was released in March 2023. In 2021, the specification changed primary terminology. The Master term was replaced with the Manager term, and the Slave term was replaced with the Subordinate term. It is worth mentioning because almost all available materials, except the specification and available IP cores, still use the old terminology. AXI gained much popularity probably because it became de facto the standard for connecting IP cores in FPGA designs utilizing AMD Xilinx or Intel chips. Both companies are the major programmable logic devices market vendors, and both offer AXI interconnect cores and functional IP cores with AXI interfaces.

The AXI protocol defines five independent channels:

- 1. write request (AW),

- 2. write data (W),

- 3. write response (B),

- 4. read request (AR),

- 5. read data (R).

Request channels carry control information that describes the nature of the data to be transferred. Having independent channels for write and read means that the master can simultaneously write and read the same slave. Write throughput is not limited by read transactions, and read throughput is not limited by write transactions. This is not true, for example, for the Wishbone bus.

The specification does not impose possible system interconnect topologies and only mentions the most popular ones:

- 1. shared request and data channels,

- 2. shared request channel and multiple data channels,

- 3. multilayer, with multiple request and data channels.

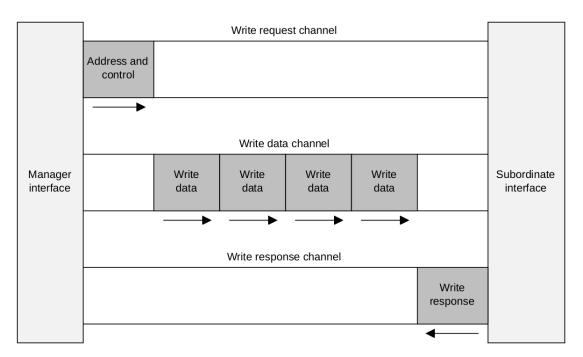

Figure 2.1 presents the AXI channel architecture of writes. A single transaction might contain multiple transfers. Write transaction completion is signaled only for a complete transaction, not for each data transfer in a transaction.

Figure 2.1: AXI channel architecture of writes [4].

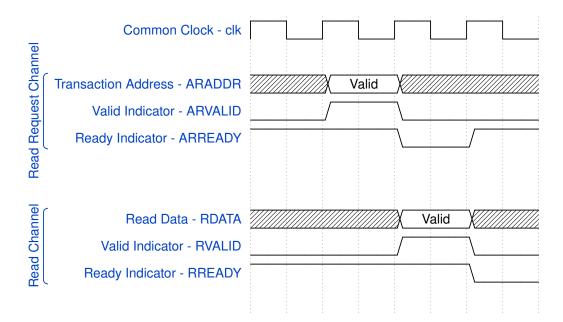

Figure 2.2 shows the timing diagram for AXI single read transaction with single data transfer and a bare minimum number of interface signals. It is the simplest possible transaction with the minimum number of channels involved. The manager drives address and valid signals in the read request channel and the ready signal in the read channel. The subordinate drives the ready signal in the read request channel and data and valid signals in the read channel. The side driving the ready signal can assert or deassert it anytime, even before valid signal assertion. This means handshaking in AXI can take as

Figure 2.2: AXI single read transaction with single data transfer.

little as one clock cycle. A transfer occurs only when both the valid and ready signals are high. The side driving the valid signal must wait for ready assertion after it asserts the valid signal. A deadlock happens if the side driving the valid signal waits for the ready signal assertion before the valid signal assertion and the side driving the ready signal waits for the valid signal assertion before the ready assertion. To prevent such scenarios, the specification states that the valid signal source is not permitted to wait until the ready signal is asserted before asserting the valid signal. The specification forbids combinatorial paths between input and output signals on the manager and subordinate sides.

The AMBA AXI specification also defines the AXI-Lite version of the protocol. The AXI-Lite is a subset of AXI where all transactions have one data transfer. It is intended for communication with register-based components and simple memories when bursts of data transfer are not advantageous.

There is also an AMBA AXI-Stream protocol defined in a separate specification [28]. AXI-Stream is a point-to-point protocol connecting a single Transmitter and a single Receiver. The terms "Master/Manager" and "Slave/Subordinate" are not used in this case, as the data always flows from the Transmitter to the Receiver. The specification of AXI-Stream describes how data is transferred but does not describe the meaning of the data. AXI-Stream is often used in data streaming applications, for example, video processing. Although defined as a separate protocol, the AXI-Stream utilizes the same valid-ready handshaking approach as the standard AXI protocol.

### 2.2 Wishbone

Wishbone bus architecture was developed by Silicore Corporation. It was put into the public domain in August 2002 by OpenCores (an organization promoting open IP cores development). Wishbone versions till revision 4 were not copyrighted, and revision 4 is copyrighted to the OpenCores. Wishbone can be freely copied and distributed.

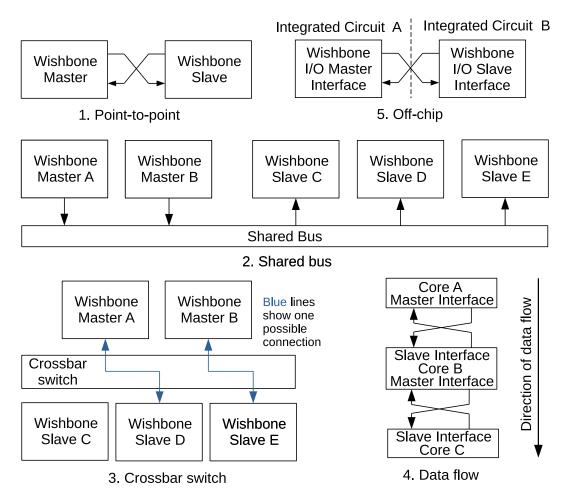

Wishbone supports various core interconnection means, including:

- 1. point-to-point,

- 2. shared bus,

- 3. crossbar switch,

- 4. data flow,

- 5. off chip.

The possible interconnections are presented in Figure 2.3.

Figure 2.3: Possible Wishbone interconnections.

Wishbone supports single read/write transactions, with possible pipelining (introduced in revision 4), block read/write transactions, and read-modify-write transactions. It also supports registered feedback transactions, which allow for better throughput.

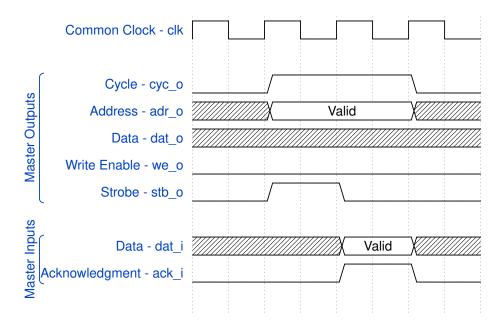

Figure 2.4 shows the timing diagram for a classic standard single read transaction with the bare minimum number of interface signals. It is the simplest possible transaction. However, it is enough to present how fundamentally different Wishbone control logic is from the AXI control logic. The transaction starts when the cycle signal is asserted by

Figure 2.4: Wishbone classic standard single read transaction.

the master on the second clock rising edge. The master also drives the address bus, write enable and asserts the strobe signal to inform the slave that signals are valid and can be read. The slave drives data on the third clock rising edge and asserts the acknowledgment signal to inform the master that the data is valid. The slave may wait before asserting the acknowledgment signal to throttle the transaction speed.

Compared to the AXI, the handshaking in Wishbone is related to the transaction as a whole. There is no separate handshaking for requests, data, and write response.

#### 2.3 Network on Chip

The network on chip is an on-chip interconnect architecture trying to overcome the limits of the traditional bus architectures. The problem was observed and reported in the late 1990s, and was initially addressed in the early years of the 21st century [29, 30, 31, 32]. The most popular drawbacks of the traditional bus architectures that NoC tries to solve include:

- 1. Limited bandwidth shared by all attached units.

- 2. Decrease of the maximum frequency with the increase of the number of modules connected to the bus. Every module adds parasitic capacitance, therefore the electrical performance degrades with the increase of modules number.

- 3. IPs interface incompatibility. The 32-bit AXI Lite master will simply not work with the 64-bit Wishbone slave in a traditional bus architecture without an extra bridge. In the NoC approach, each network node can have an individual interface for local register access.

- 4. Coupled transaction, transport, and physical activities. Changes to the bus physical implementation can have profound ripple effects upon the implementation of the higher-level bus behaviors. NoC distinguishes transaction, transport, and physical layers that can be adjusted or improved independently.

However, NoC is mainly used in high bandwidth performance critical heterogeneous SoC applications. Even homogeneous designs focused on accelerating the processing of gigabytes or terabytes of data (usually implemented using the HLS technique) do not use NoC but rather different types of AXI interfaces depending on the nature and amount of data being exchanged between modules [33]. This is because NoC is not free of drawbacks. The most popular ones are:

- 1. Latency increase due to the internal network connections and routing algorithms.

- 2. Increased resource utilization compared to the traditional bus architectures.

- 3. Increased overall system complexity.

There are numerous different NoC topologies [34, 35, 36, 37, 38, 39]. The most popular ones include ring, octagon, star, mesh, torus, folded torus, butterfly, binary tree, fat tree, cube, crossed cube, hypercube, reduced hypercube, reduced mesh and cluster-based hybrid, mesh connected ring, and cmesh.

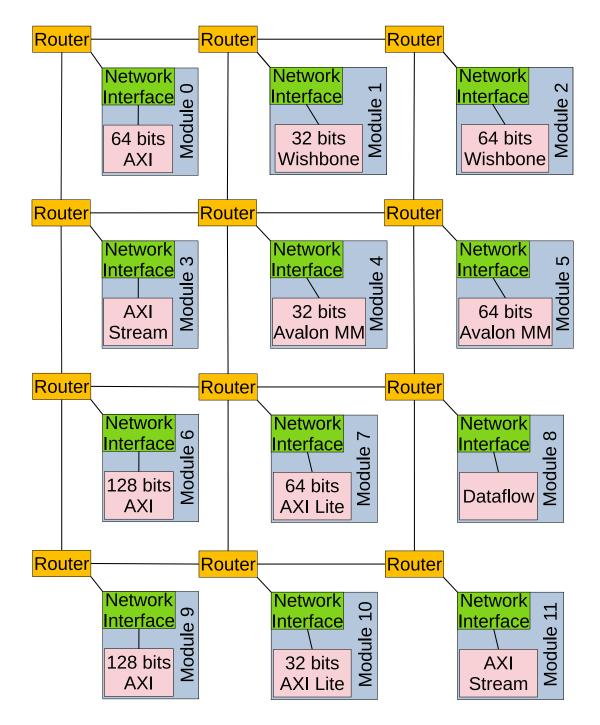

Although the NoC architecture was inspired by well-known computer networks such as LAN or WAN, it differs significantly from them. This is because the implementing the protocols used in these networks, such as IP [40] or TCP [41], would consume a relatively large amount of resources and require significant buffering capabilities. NoC packet typically consists of a header and payload data. The header must include at least the address of the destination node, but it often also includes data length, data tags, and the address of the source node. How the data is routed via the network depends on the routing algorithm. Although the macro-level architecture of the NoC differs significantly from the traditional bus architecture, the packet data still has to be somehow distributed inside the module attached to the network via the network interface. There are two standard

ways to achieve this. The first one is dataflow communication, and the second one is address space communication. This is exactly what traditional buses were designed for. So, in the end, the traditional bus architectures are still used within the NoC architectures. However, their scope is limited to the single network nodes. Figure 2.5 presents an example 12 nodes network on chip with the mesh topology.

Figure 2.5: Example 12 nodes mesh network on chip.

# 3 Prior art

This chapter presents the current state of the art. The term "tool" is used for all solutions, although not all are strictly tools. Moreover, some are standalone entities, while others are a part of more extensive frameworks. Each tool has been designed and implemented by different teams. Although their main goal is the same, they sometimes accentuate diverse areas. As a result, relative comparison is not always straightforward. This is why they are rather matched against a generic template. Nonetheless, none of the available solutions offers a functional view of data placed in the registers. They are registers-centric. The order of analysis is alphabetical.

#### 3.1 Existing tools

Register-centric approaches can be divided into two classes depending on the data they produce. The first class, as the output data, produces information on register addresses, masks, and bit shifts. The second class abstracts registers and bit fields as objects. The user does not explicitly use addresses, masks, and bit shifts but calls methods for reading and writing particular registers and bit fields. Instead of providing methods for reading and writing, some solutions prefer operators overloading, for example [42]. The second class is safer to use as it eliminates mistakes caused, for example, by applying bit shift of bit field B.

It is important to mention that all described tools and solutions are in continuous development, so some of their features might have changed, or new features might have been added since they were described. It is also worth mentioning that if tool T claims support for feature F or language L, then it might not be full support, as all such tools are implemented incrementally. It does not indicate the weakness of the tools but rather shows a pragmatic approach to the problem. There would be no technical progress in the described field if the tools were usable only when they were 100 % complete.

#### 3.1.1 airhdl

The airhdl [43] is a web-based AXI4 VHDL/SystemVerilog register generator tool. It also has a command line version, requiring Java runtime version 8 or higher, accepting register specification in JSON [44] format. It supports code generation for SystemVerilog, VHDL, C/C++, HTML [45] or Markdown documentaiton or transformation to IP-XACT XML [46] format. The tool is closed source, and any plan except the Free one is paid. The main website has a demo video upon which it is clear that the tool follows the register-centric approach. The user explicitly defines registers and bit fields. The generated C header file contains macros defining addresses, offsets, and masks.

#### 3.1.2 Address Generator for Wishbone

The AGWB [3, 47], the successor of addr\_gen [48], facilitates the automated generation of the control system's HDL and software components based on the XML system description. It supports code generation for VHDL, C, Python, Forth, XML register map, and HTML for documentation.

Listing 8 presents an example AGWB register description in XML format. This snippet is taken directly from the DAQ readout chain for the STS being prepared for the CBM experiment at GSI Darmstadt.

```

<block name="hctsp software command slot">

<creg name="control" stb="1" default="0x0">

<field name="chip_address"

width="4"/>

<field name="downlink mask"

width="12"/>

<field name="group_mask"

width="8"/>

<field name="sequence_number" width="4"/>

</creg>

<creg name="control_frame" reps="2" default="0x0">

<field name="request type"

width="2"/>

<field name="request_payload" width="15"/>

<field name="crc"

width="15"/>

</creg>

</block>

```

Listing 8: Example AGWB description in XML format.

The hctsp\_software\_command\_slot block has three control registers with an extra strobe signal associated with the control register. What is not seen and can not be deduced from the description is that all three control registers constitute a broader context. Namely, they are all used to pass arguments to the procedure sending commands to the set of front-end ASICs. Which front-end ASICs receive the command depends on the values of

the chip\_address, downlink\_mask, and group\_mask. None of the three control registers makes sense without the remaining two registers. What is more, as the control control register has an associated strobe signal (stb="1") it must be written as the last of the three registers. However, as the approach is register-centric, the correct write access order must be coded manually. It leaves room for the programmer's mistakes.

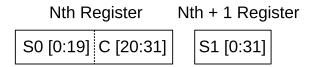

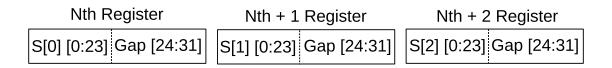

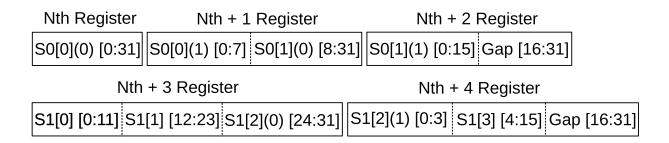

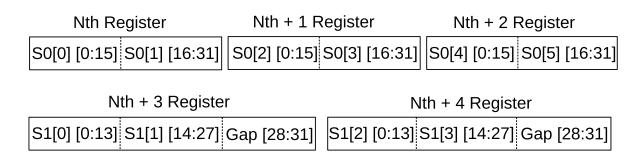

Listing 9 shows the VHDL interface of the Software Command Slot entity. The set\_pending\_i port is connected to the strobe signal of the control register. The clear\_pending\_i port in the actual design is driven by the command consumer logic, but for co-simulation purposes, it was connected to the testbench register with an associated strobe signal. The definitions of t\_command and t\_command\_request record types are not shown. However, all fields belonging to these types are presented in figures 3.1 and 3.2.

```

entity Software_Command_Slot is

port (

clk_40_i : in std_logic;

set_pending_i : in std_logic;

clear_pending_i : in std_logic;

downlink_mask_i : in std_logic_vector(11 downto 0);

group_mask_i : in std_logic_vector(7 downto 0);

command_i : in t_command;

command_request_o : out t_command_request := C_EMPTY_COMMAND_REQUEST

);

end entity;

```

Listing 9: Software Command Slot VHDL entity interface.

Listing 10 shows the creation of write commands for Python co-simulation testbench. A single write command consists of two control frames. The first control frame contains the register address as the payload, and the second one contains data. The provided **sequence\_number** is the sequence number of the first control frame, the second control frame within the command must have a sequence number increased by one compared to the first control frame.

```

write_commands = [

Command(

downlink_mask = 0x30,

group_mask = 0x8,

chip_address = 3,

sequence_number = 0,

request_types = (WRADDR, WRDATA),

register_address = 0x4A,

data = 0x31,

),

Command(

downlink_mask = 0x1D0,

group_mask = OxAB,

chip_address = OxF,

sequence_number = OxD,

request_types = (WRADDR, WRDATA),

register_address = 0xFF9,

data = 0x75,

),

]

```

Listing 10: Snippet of Python code with write command objects creation for Software Command Slot.

Listing 11 presents the Python method with an invalid order of register writes. As the access order has to be implemented manually, it is relatively easy to write the control register before the control\_frame registers by mistake. If the control register is written before control\_frame registers, the system "almost works."

```

def send(self, handle):

handle.control.writeb(

(self.sequence_number << 24 ) |

(self.group_mask << 16) |

(self.downlink_mask << 16) |

(self.downlink_mask << 4) |

self.chip_address

)

for i in range(0,2):

handle.control_frame[i].writeb(

(self.crcs[i] << 17) |

(self.crcs[i] << 17) |

(self.payloads[i] << 2) |

self.request_types[i]

)

```

Listing 11: Python method sending command to the Software Command Slot - invalid write order.

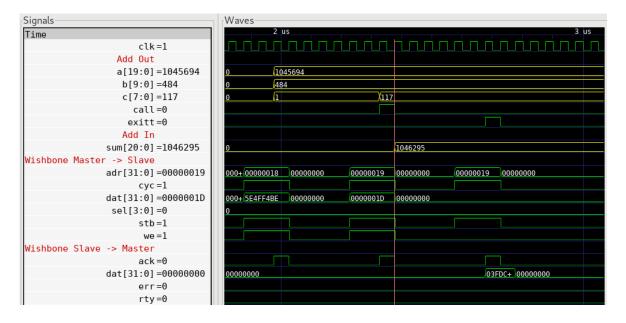

Figure 3.1 presents waveforms for signals connected to the Software Command Slot entity ports in case of invalid write order. When the command request is marked as pending, the **typee**, **payload** and **crc** attributes of both control frames are not yet valid (waveforms ). The behavior depends on when the command request consumer samples the data. If sampling happens after the **typee**, **payload**, and **crc** are updated, the system works correctly. However, if sampling happens before the update, then the system works incorrectly. The first command results in a CRC error. However, later commands are sent correctly with an extra one command delay unless the set of destination front-end ASICs changes. In such cases, valid commands are sent to the invalid set of ASICs, and no error is reported. Such bugs can be complex and time-consuming to debug, as there is implicit state storage between commands in case of incorrect register write order. This kind of mistake happened to the author during the development and made him think there must be a better way to describe data stored in the registers.

| Signals                                | Waves   |     |        |        |       |       |     |       |     |        |

|----------------------------------------|---------|-----|--------|--------|-------|-------|-----|-------|-----|--------|

| Time                                   | .00 ns  | 200 | ns 300 | 9 ns 4 | 00 ns | 500 n | ; 6 | 00 ns | 70  | 9 ns 1 |

| clk 40 i=1                             |         | hr  | mm     | INN    | ллл   | ார    | ՄՄ  | ாப    |     |        |

| set pending i=0                        |         |     |        |        |       |       |     |       |     |        |

| clear pending i=0                      |         |     |        |        | 1     |       |     |       |     |        |

| command i                              |         |     |        |        |       |       |     |       |     |        |

| downlink_mask_i[11:0]=1D0              | 000 (03 | 30  |        |        |       | X     | DØ  |       |     |        |

| group_mask_i[7:0]=AB                   | 00 08   | 3   |        |        |       | )/    | B   |       |     |        |

| command_i.control_frames(0)            |         |     |        |        |       |       |     |       |     |        |

| chip_address[3:0]=F                    | 0 3     |     |        |        |       | ),    |     |       |     |        |

| sequence_number[3:0]=D                 | 0       |     |        |        |       |       | )   |       |     |        |

| typee=wraddr                           | no_op   |     | wraddr |        |       |       |     |       |     |        |

| payload[14:0]=004A                     | 0000    |     | 004A   |        |       |       |     | 0FF9  |     |        |

| crc[14:0]=1734                         | 0000    |     | 1734   |        |       |       |     | 62D8  |     |        |

| <pre>command_i.control_frames(1)</pre> |         |     |        |        |       |       |     |       |     |        |

| chip_address[3:0]=F                    | 0 3     |     |        |        |       | ) F   |     |       |     |        |

| sequence_number[3:0]=E                 | 1       |     |        |        |       | )(E   |     |       |     |        |

| typee=wrdata                           | no_op   |     |        | vrdata |       |       |     |       |     |        |

| payload[14:0]=0031                     | 0000    |     |        | 031    |       |       |     |       | 007 | '5     |

| crc[14:0]=00D2                         | 0000    |     |        | 00D2   |       |       |     |       | 64F | 1      |

| command_request_o                      |         |     |        |        |       |       |     |       |     |        |

| pending=1                              |         |     |        |        |       |       |     |       |     |        |

| downlink_mask[11:0]=1D0                | 000     | 030 |        |        |       |       | 1D0 |       |     |        |

| group_mask[7:0]=AB                     | 00      | 08  |        |        |       |       | AB  |       |     |        |

| command_request_o.control_frames(0)    |         |     |        |        |       |       |     |       |     |        |

| chip_address[3:0]=F                    | 0       | 3   |        |        |       |       | F   |       |     |        |

| sequence_number[3:0]=D                 | 0       |     |        |        |       |       | D   |       |     |        |

| typee=wraddr                           | no_op   |     | wraddr |        |       |       |     |       |     |        |

| payload[14:0]=004A                     | 0000    |     | 004A   |        |       |       |     | OFF   |     |        |

| crc[14:0]=1734                         | 0000    |     | 1734   |        |       |       |     | 620   | 08  |        |

| command_request_o.control_frames(1)    |         |     |        |        |       |       |     |       |     |        |

| chip_address[3:0]=F                    | 0       | 3   |        |        |       |       | F   |       |     |        |

| sequence_number[3:0]=E                 | 1       |     |        |        |       |       | E   |       |     |        |

| typee=wrdata                           | no_op   |     |        | wrdata |       |       |     |       |     |        |

| payload[14:0]=0031                     | 0000    |     |        | 0031   |       |       |     |       |     | 0075   |

| crc[14:0]=00D2                         | 0000    |     |        | 00D2   |       |       |     |       |     | 64F1   |

Figure 3.1: Software Command Slot entity port signal waveforms - invalid write order.

Listing 12 shows the Python method with a valid order of register writes, and figure 3.2 presents waveforms for signals connected to the Software Command Slot entity ports in case of valid write order. All attributes of both control frames are already valid when the command request pending signal is asserted. The result does not depend on the command consumer sampling time.

```

def send(self, handle):

for i in range(0,2):

handle.control_frame[i].writeb(

(self.crcs[i] << 17) |

(self.payloads[i] << 2) |

self.request_types[i]

)

handle.control.writeb(

(self.sequence_number << 24 ) |

(self.group_mask << 16) |

(self.downlink_mask << 4) |

self.chip_address

)</pre>

```

Listing 12: Python method sending command to the Software Command Slot - valid write order.

| Signals                                | Waves        |        |        |           |          |        |          |

|----------------------------------------|--------------|--------|--------|-----------|----------|--------|----------|

| Time                                   | 100 ns       | 200    | ns 300 | ns 400 ns | 500 ns ( | 600 ns | 700 ns 8 |

| clk_40_i=1                             | ГП           |        |        |           |          |        | ւլուս    |

| set_pending_i=0                        |              |        |        |           |          |        |          |

| clear_pending_i=0                      |              |        |        |           |          |        |          |

| command_i                              |              |        |        |           |          |        |          |

| downlink_mask_i[11:0]=1D0              | 000          |        | 03     | 0         |          | )1     | .DØ      |

| group_mask_i[7:0]=AB                   | 00           |        | 08     |           |          | )A     | ιB       |

| <pre>command_i.control_frames(0)</pre> |              |        |        |           |          |        |          |

| chip_address[3:0]=F                    | 0            |        | 3      |           |          | ), F   |          |

| sequence_number[3:0]=D                 | 0            |        |        |           |          |        |          |

| typee=wraddr                           | no_op 🕅      | wraddr |        |           |          |        |          |

| payload[14:0]=0FF9                     | 0000         | 004A   |        |           | 0FF9     |        |          |

| crc[14:0] =62D8                        | 0000         | 1734   |        |           | 62D8     |        |          |

| <pre>command_i.control_frames(1)</pre> |              |        |        |           |          |        |          |

| chip_address[3:0]=F                    | Θ            |        | 3      |           |          | ) F    |          |

| sequence_number[3:0]=E                 | 1            |        |        |           |          | )e     |          |

| typee=wrdata                           | no_op        |        | wrdata |           |          |        |          |

| payload[14:0]=0075                     | 0000         |        | 0031   |           |          | 0075   |          |

| crc[14:0]=64F1                         | 0000         |        | 00D2   |           |          | 64F1   |          |

| command_request_o                      |              |        |        |           |          |        |          |

| pending=1                              |              |        |        |           |          |        |          |

| downlink_mask[11:0]=1D0                | 000          |        |        | 030       |          |        | 1D0      |

| group_mask[7:0]=AB                     | 00           |        |        | 08        |          |        | AB       |

| command_request_o.control_frames(0)    |              |        |        |           |          |        |          |

| chip_address[3:0]=F                    | Θ            |        |        | 3         |          |        | F        |

| <pre>sequence_number[3:0] =D</pre>     | Θ            |        |        |           |          |        | D        |

| typee=wraddr                           | <u>no_op</u> | wradd  | r      |           |          |        |          |

| payload[14:0]=0FF9                     | 0000         | 004A   |        |           | 0FF9     |        |          |

| crc[14:0]=62D8                         | 0000         | 1734   |        |           | 62D8     |        |          |

| command_request_o.control_frames(1)    |              |        |        |           |          |        |          |

| chip_address[3:0]=F                    | Θ            |        |        | 3         |          |        | F        |

| sequence_number[3:0]=E                 | 1            |        |        |           |          |        | E        |

| typee=wrdata                           | no_op        |        | wrdata |           |          |        |          |

| payload[14:0]=0075                     | 0000         |        | 0031   |           |          | 0075   |          |

| crc[14:0]=64F1                         | 0000         |        | 00D2   |           |          | 64F1   |          |

Figure 3.2: Software Command Slot entity port signal waveforms - valid write order.

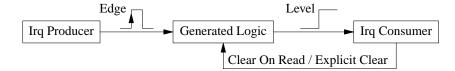

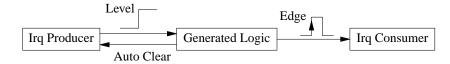

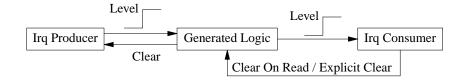

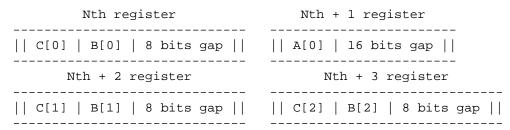

### 3.1.3 AutoFPGA